产品分类

产品标签

Fmuser网站

- es.fmuser.net

- it.fmuser.net

- fr.fmuser.net

- de.fmuser.net

- af.fmuser.net ->荷兰语

- sq.fmuser.net ->阿尔巴尼亚人

- ar.fmuser.net ->阿拉伯语

- hy.fmuser.net - >亚美尼亚

- az.fmuser.net ->阿塞拜疆

- eu.fmuser.net ->巴斯克

- be.fmuser.net ->白俄罗斯语

- bg.fmuser.net - >保加利亚

- ca.fmuser.net ->加泰罗尼亚语

- zh-CN.fmuser.net ->中文(简体)

- zh-TW.fmuser.net - >中国(繁体)

- hr.fmuser.net ->克罗地亚语

- cs.fmuser.net ->捷克

- da.fmuser.net ->丹麦语

- nl.fmuser.net - >荷兰

- et.fmuser.net ->爱沙尼亚语

- tl.fmuser.net ->菲律宾

- fi.fmuser.net ->芬兰语

- fr.fmuser.net - >法国

- gl.fmuser.net ->加利西亚语

- ka.fmuser.net ->乔治亚

- de.fmuser.net ->德语

- el.fmuser.net - >希腊

- ht.fmuser.net ->海地克里奥尔语

- iw.fmuser.net ->希伯来语

- hi.fmuser.net ->印地语

- hu.fmuser.net - >匈牙利

- is.fmuser.net ->冰岛语

- id.fmuser.net ->印尼语

- ga.fmuser.net ->爱尔兰

- it.fmuser.net - >意大利

- ja.fmuser.net ->日语

- ko.fmuser.net ->韩文

- lv.fmuser.net ->拉脱维亚

- lt.fmuser.net - >立陶宛

- mk.fmuser.net ->马其顿语

- ms.fmuser.net ->马来语

- mt.fmuser.net ->马耳他语

- no.fmuser.net - >挪威

- fa.fmuser.net ->波斯语

- pl.fmuser.net ->波兰语

- pt.fmuser.net ->葡萄牙语

- ro.fmuser.net - >罗马尼亚

- ru.fmuser.net ->俄语

- sr.fmuser.net ->塞尔维亚语

- sk.fmuser.net ->斯洛伐克

- sl.fmuser.net - >斯洛文尼亚

- es.fmuser.net ->西班牙语

- sw.fmuser.net ->斯瓦希里语

- sv.fmuser.net ->瑞典语

- th.fmuser.net - >泰国

- tr.fmuser.net ->土耳其语

- uk.fmuser.net ->乌克兰语

- ur.fmuser.net ->乌尔都语

- vi.fmuser.net - >越南

- cy.fmuser.net ->威尔士语

- yi.fmuser.net - >意第绪语

什么是半加器:电路图及其应用

Date:2021/10/18 21:55:58 Hits:

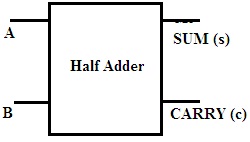

半加器是一种基本的数字电路。 早些时候在模拟电路中执行了各种操作。 在发现数字电子之后,在其中进行了类似的操作。 数字系统被认为是有效且可靠的。 在各种运算中,最突出的运算之一是算术。 它包括加法、减法、乘法和除法。 然而,众所周知,它可能是一台计算机,任何像计算器这样的电子设备都可以进行数学运算。 这些操作由二进制值组成。由于其中存在某些电路,这是可能的。 这些电路被称为二进制加法器和减法器。 这种类型的电路是为二进制码、Excess-3 码和其他码而设计的。 进一步的二进制加法器分为两种类型。 它们是: 半加器和全加器什么是半加器? 用于对二进制数执行加法的数字电子电路被定义为半加器。 加法过程是否定的,唯一的区别是所选择的数字系统。 二进制编号系统中只有 0 和 1。 数字的权重完全取决于二进制数字的位置。 在1和0中,1作为最大的数字,0作为较小的数字。 这个加法器的框图是 半加器半加器电路图半加器由两个输入组成并产生两个输出。 它被认为是最简单的数字电路。 该电路的输入是要对其执行加法的位。 获得的输出是和和进位。

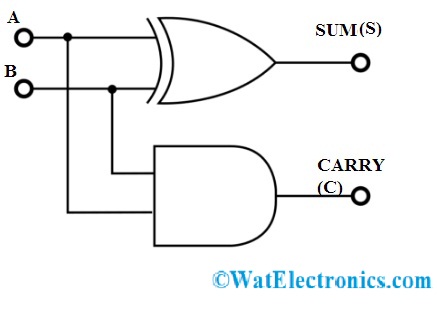

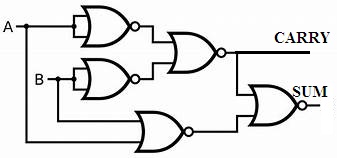

半加器半加器电路图半加器由两个输入组成并产生两个输出。 它被认为是最简单的数字电路。 该电路的输入是要对其执行加法的位。 获得的输出是和和进位。  半加器该加法器的电路由两个门组成。 它们是 AND 和 XOR 门。 电路中存在的两个门的应用输入相同。 但是输出来自每个门。 XOR 门的输出称为 SUM,AND 的输出称为 CARRY。半加器真值表要获得获得的输出与应用输入的关系,可以使用称为真值表的表进行分析。

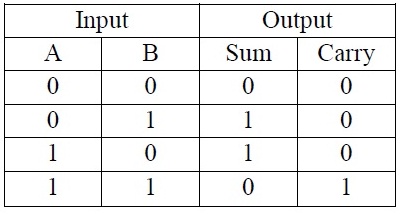

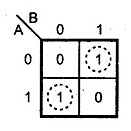

半加器该加法器的电路由两个门组成。 它们是 AND 和 XOR 门。 电路中存在的两个门的应用输入相同。 但是输出来自每个门。 XOR 门的输出称为 SUM,AND 的输出称为 CARRY。半加器真值表要获得获得的输出与应用输入的关系,可以使用称为真值表的表进行分析。 半加器真值表 从上面的真值表中可以看出以下几点:如果 A=0,B=0 即应用的两个输入都是 0。那么输出 SUM 和 CARRY 都是 0。在应用的两个输入中,如果有任何一个输入为 1,则 SUM 将为 e1,但 CARRY 为 0。如果两个输入均为 1,则 SUM 将等于 0,而 CARRY 将等于 1。基于应用的输入,半加器继续运算加法等式 此类电路的等式可以通过乘积总和 (SOP) 和总和 (POS) 的概念来实现。 这种类型电路的布尔方程确定了所应用的输入与获得的输出之间的关系。为了确定方程,根据真值表值绘制了 k 映射。 它由两个方程组成,因为其中使用了两个逻辑门。进位的 k-map 是

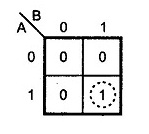

半加器真值表 从上面的真值表中可以看出以下几点:如果 A=0,B=0 即应用的两个输入都是 0。那么输出 SUM 和 CARRY 都是 0。在应用的两个输入中,如果有任何一个输入为 1,则 SUM 将为 e1,但 CARRY 为 0。如果两个输入均为 1,则 SUM 将等于 0,而 CARRY 将等于 1。基于应用的输入,半加器继续运算加法等式 此类电路的等式可以通过乘积总和 (SOP) 和总和 (POS) 的概念来实现。 这种类型电路的布尔方程确定了所应用的输入与获得的输出之间的关系。为了确定方程,根据真值表值绘制了 k 映射。 它由两个方程组成,因为其中使用了两个逻辑门。进位的 k-map 是  K-Map AND Gate从AND门得到CARRY的输出方程。C=A.BSUM的布尔表达式是通过SOP形式实现的。 因此 SUM 的 K-map 是

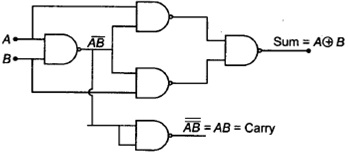

K-Map AND Gate从AND门得到CARRY的输出方程。C=A.BSUM的布尔表达式是通过SOP形式实现的。 因此 SUM 的 K-map 是 K-Map for Sum (XOR) 确定的方程为 S= A⊕ B 应用这个基本加法器的应用如下 为了对二进制位进行加法,计算机中存在的算术和逻辑单元更喜欢这种加法器电路。半加器电路的组合导致形成全加器电路。这些逻辑电路在计算器的设计中是首选。为了计算地址和表格,这些电路是首选。这些电路不仅仅是加法,而是能够处理数字电路中的各种应用。 此外,这成为数字电子学的核心。 VHDL 代码半加器电路的 VHDL 代码是库 ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;half_adder 的架构数据 isbeginsum<= a xor b;carry <= a and b;end data;FAQs1. 加法器是什么意思?唯一目的是执行加法的数字电路称为加法器。 这些是 ALU 的主要组件。 除了各种格式的数字之外,加法器还可以操作。 加法器的输出是和和进位。2。 半加器的局限性是什么?前一位产生的进位不能相加是这个加法器的局限性。 为了执行多个位的加法,这些电路不能被优选。3. 如何使用或非门实现半加器?这种类型的加法器的实现也可以通过使用或非门来完成。 这是另一个万能之门。

K-Map for Sum (XOR) 确定的方程为 S= A⊕ B 应用这个基本加法器的应用如下 为了对二进制位进行加法,计算机中存在的算术和逻辑单元更喜欢这种加法器电路。半加器电路的组合导致形成全加器电路。这些逻辑电路在计算器的设计中是首选。为了计算地址和表格,这些电路是首选。这些电路不仅仅是加法,而是能够处理数字电路中的各种应用。 此外,这成为数字电子学的核心。 VHDL 代码半加器电路的 VHDL 代码是库 ieee;use ieee.std_logic_1164.all;entity half_adder isport(a,b: in bit; sum,carry:out bit);end half_adder ;half_adder 的架构数据 isbeginsum<= a xor b;carry <= a and b;end data;FAQs1. 加法器是什么意思?唯一目的是执行加法的数字电路称为加法器。 这些是 ALU 的主要组件。 除了各种格式的数字之外,加法器还可以操作。 加法器的输出是和和进位。2。 半加器的局限性是什么?前一位产生的进位不能相加是这个加法器的局限性。 为了执行多个位的加法,这些电路不能被优选。3. 如何使用或非门实现半加器?这种类型的加法器的实现也可以通过使用或非门来完成。 这是另一个万能之门。 使用 NOR 门的半加器 4。 如何使用与非门实现半加器?与非门是通用门的一种。 这表明使用与非门可以进行任何类型的电路设计。

使用 NOR 门的半加器 4。 如何使用与非门实现半加器?与非门是通用门的一种。 这表明使用与非门可以进行任何类型的电路设计。 半加器从上述电路中,可以通过将一个与非门的输出作为另一个与非门的输入应用于输入来生成进位输出。 这对于从与门获得的输出来说是很熟悉的。 SUM 的输出方程可以通过将初始与非门的输出以及 A 和 B 的各个输入应用于进一步的与非门来生成。 最后,这些与非门获得的输出再次应用于该门。 因此生成了 SUM 的输出。因此,数字电路中的基本加法器可以通过使用各种逻辑门来设计。 但多位加法变得复杂,被认为是半加器的局限性。 你能描述在任何实际计数器中哪个 IC 用于递增操作吗?

半加器从上述电路中,可以通过将一个与非门的输出作为另一个与非门的输入应用于输入来生成进位输出。 这对于从与门获得的输出来说是很熟悉的。 SUM 的输出方程可以通过将初始与非门的输出以及 A 和 B 的各个输入应用于进一步的与非门来生成。 最后,这些与非门获得的输出再次应用于该门。 因此生成了 SUM 的输出。因此,数字电路中的基本加法器可以通过使用各种逻辑门来设计。 但多位加法变得复杂,被认为是半加器的局限性。 你能描述在任何实际计数器中哪个 IC 用于递增操作吗?

留言

邮件列表

评论载入中...